晶體振蕩器相位誤差自動校正快速啟動技術實現突破

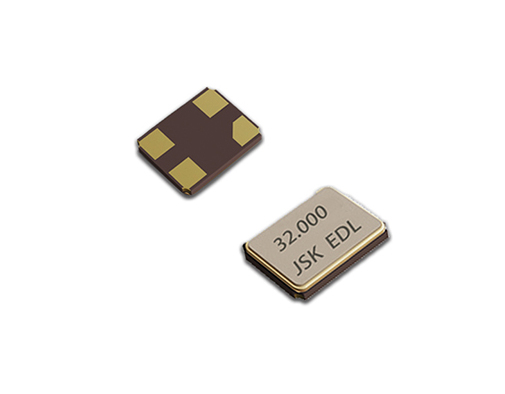

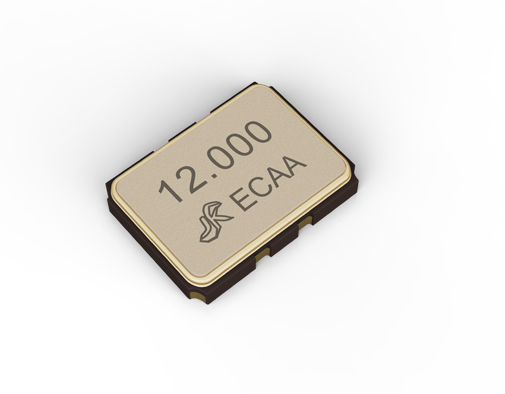

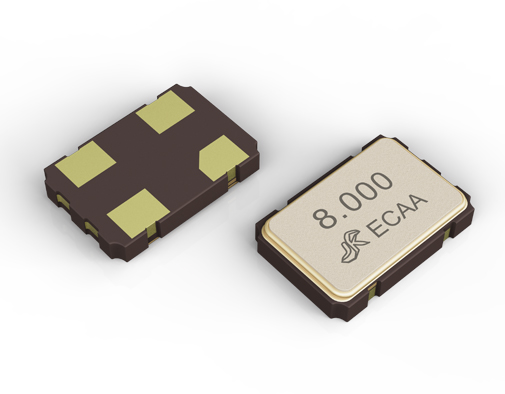

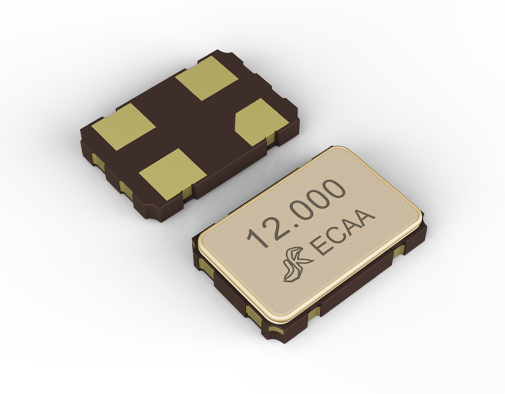

晶體振蕩器的啟動時間影響了系統的數據收發時間間隔,對于采用占空比工作模式的系統功耗具有決定性作用。隨著物聯網設備的飛速發展與低功耗應用場景的普及,快速啟動晶體振蕩器的作用至關重要。

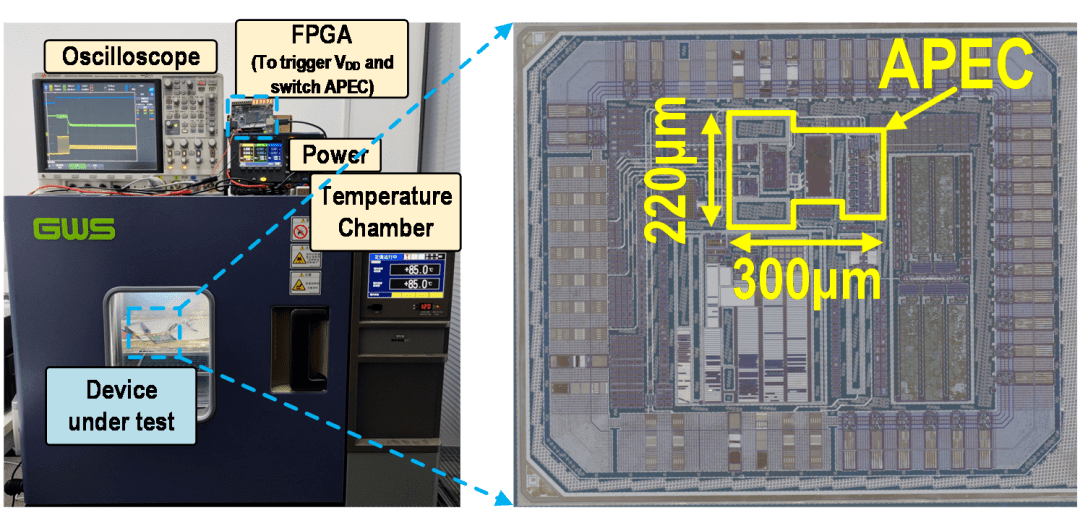

南京郵電大學集成電路科學與工程學院(產教融合學院)郭宇鋒教授、蔡志匡教授團隊在集成電路設計領域取得新進展,研發了一款基于相位誤差自動校正技術的快速啟動晶體振蕩器芯片,該款芯片實現了大頻偏注入條件下的快速啟動,突破了對注入信號頻率精度的嚴格限制,相關成果近日發表在第70屆InternationalSolidStateCircuitsConference(ISSCC)上,并入選會議Demo演示。該會議是集成電路設計領域的最高級別學術會議,素有“集成電路領域的奧林匹克”之稱。該篇論文的發表,標志著南京郵電大學成為國內第11家在ISSCC會議發表論文的大陸高校,國內首家在ISSCC會議發表論文的省屬高校。

相位誤差自動校正技術概念

據悉,高頻晶體振蕩器產生的參考時鐘屬于周期開啟的模塊,為系統中的其他模塊提供參考頻率。因此其啟動時間的長短,對于占空比工作系統的功耗影響較大,300μs以上的啟動時間便可增加低功耗藍牙系統15%的功耗開銷。因此,參考時鐘的啟動時間是限制系統功耗進一步降低的瓶頸。

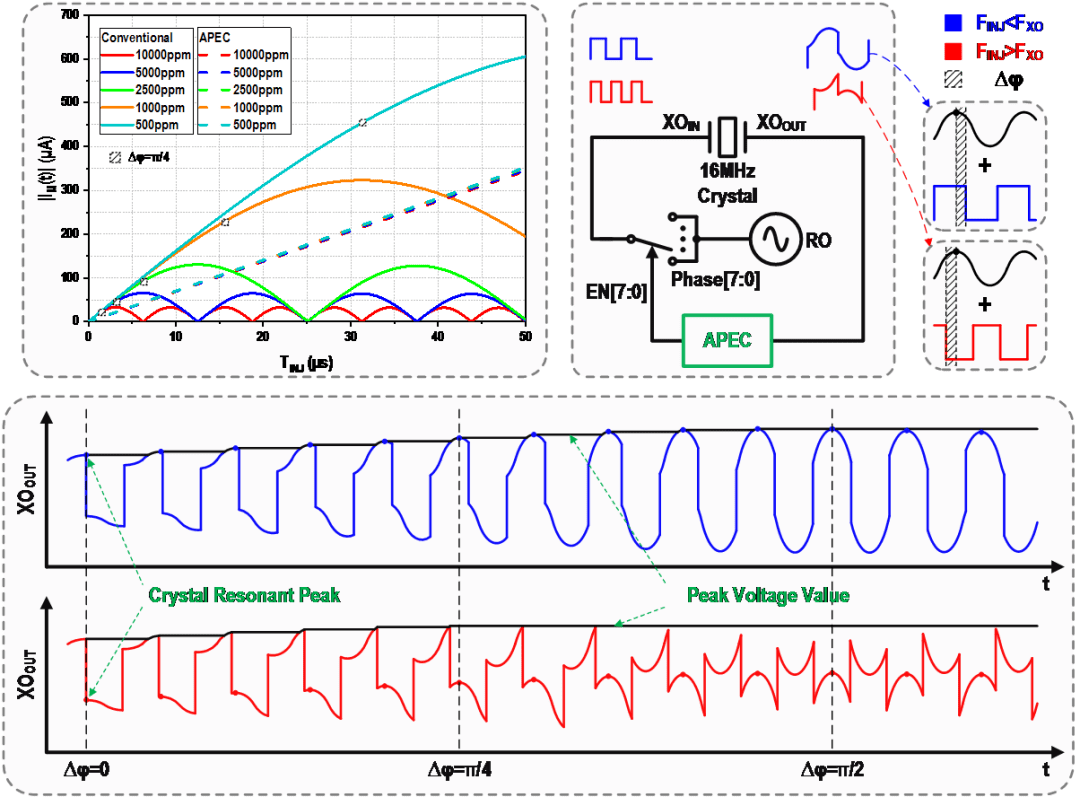

對于高頻晶體振蕩器啟動時間過長及注入效率問題,目前效率最高的同頻注入技術仍然存在著一些棘手的問題。同頻注入技術需要一個頻率精準(誤差<5000ppm)的片內注入信號源,但在實際中,該信號源頻率受PVT影響無法做到十分精準和穩定,和晶體本征振蕩頻率之間存在頻率偏差,也簡稱為頻偏。頻偏會在注入過程中積分成相位差。當這個相位差不斷累積,注入效率也就會逐漸降低,甚至出現抑制晶體啟動的情況。而如果要實現超高精準度(<1000ppm)的片內注入信號源,就意味著設計難度和所需控制字劇增,以及芯片在量產時的trim成本難以承受。因而,如何在較大的頻偏下實現高效的能量注入與晶振的快速啟動,就成為解決該問題的關鍵因素。

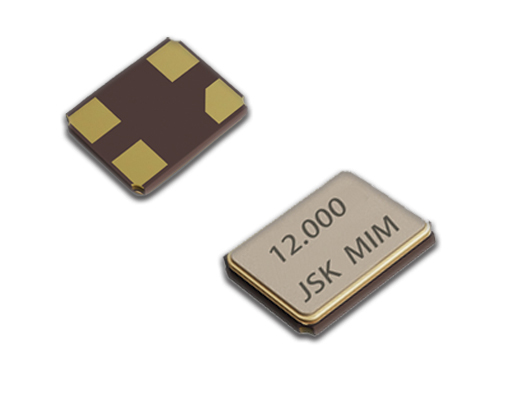

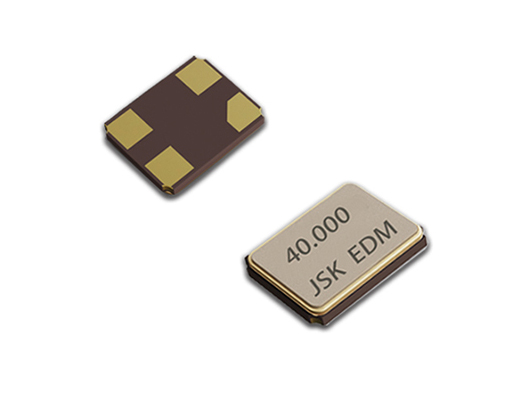

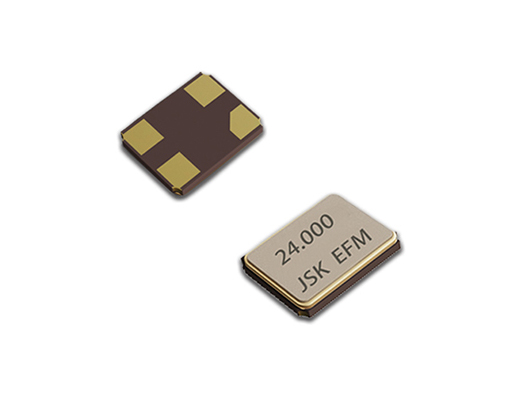

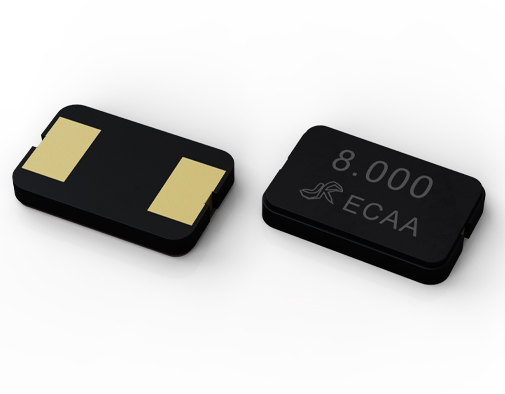

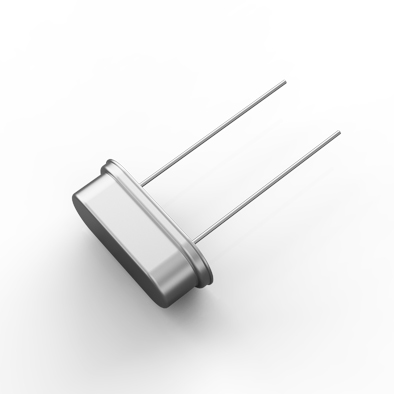

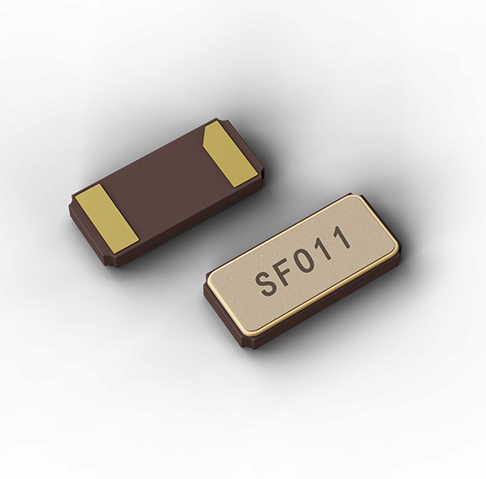

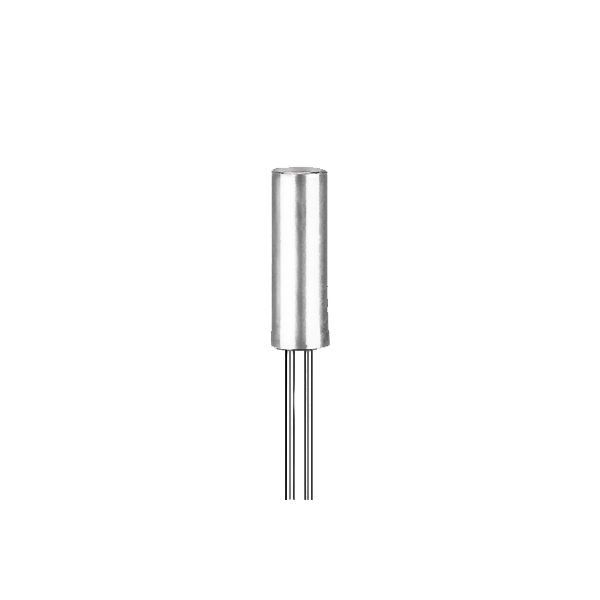

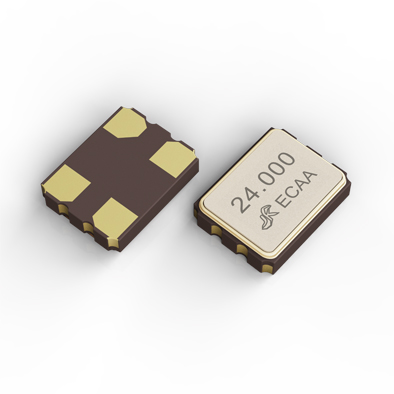

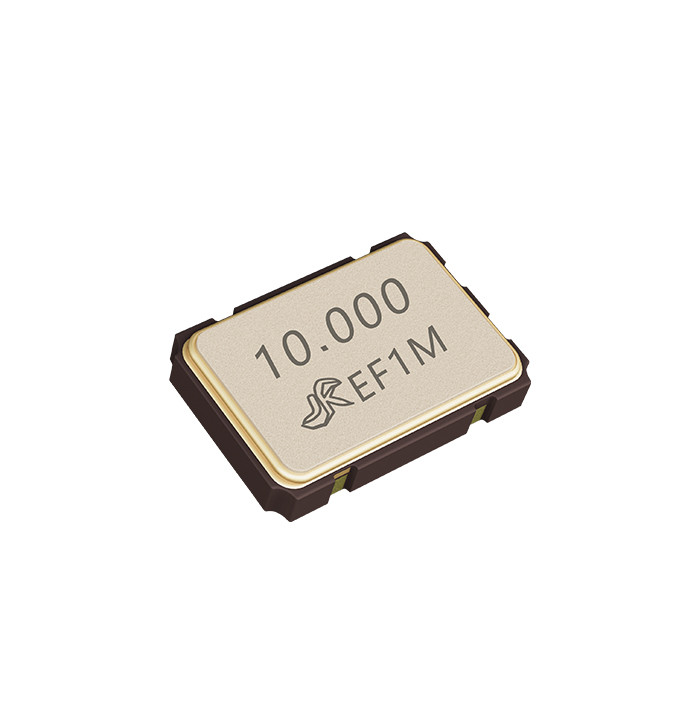

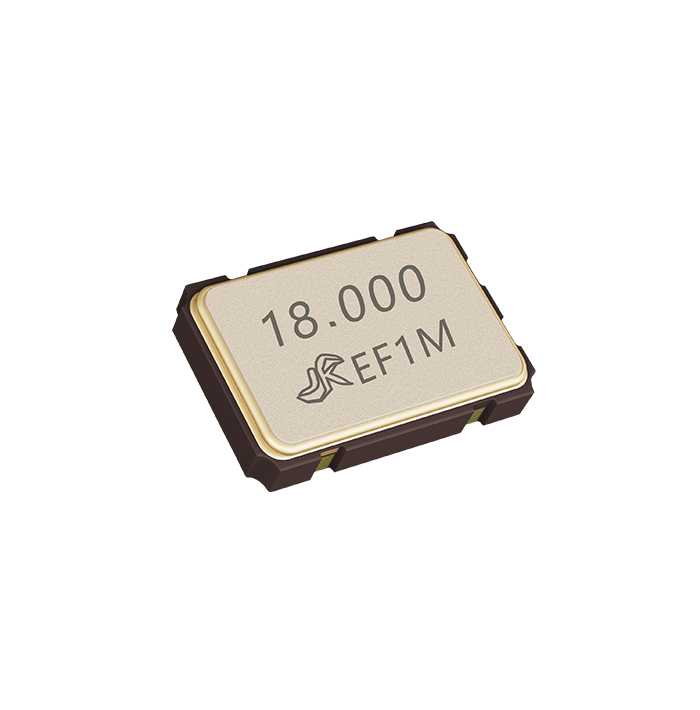

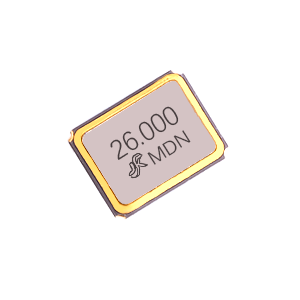

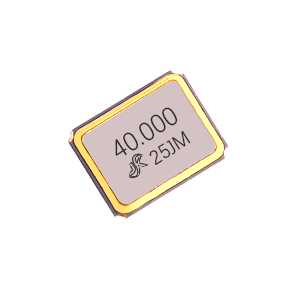

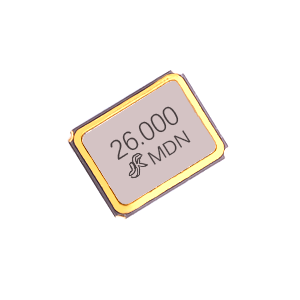

基于相位誤差自動校正技術的快速啟動晶體振蕩器芯片

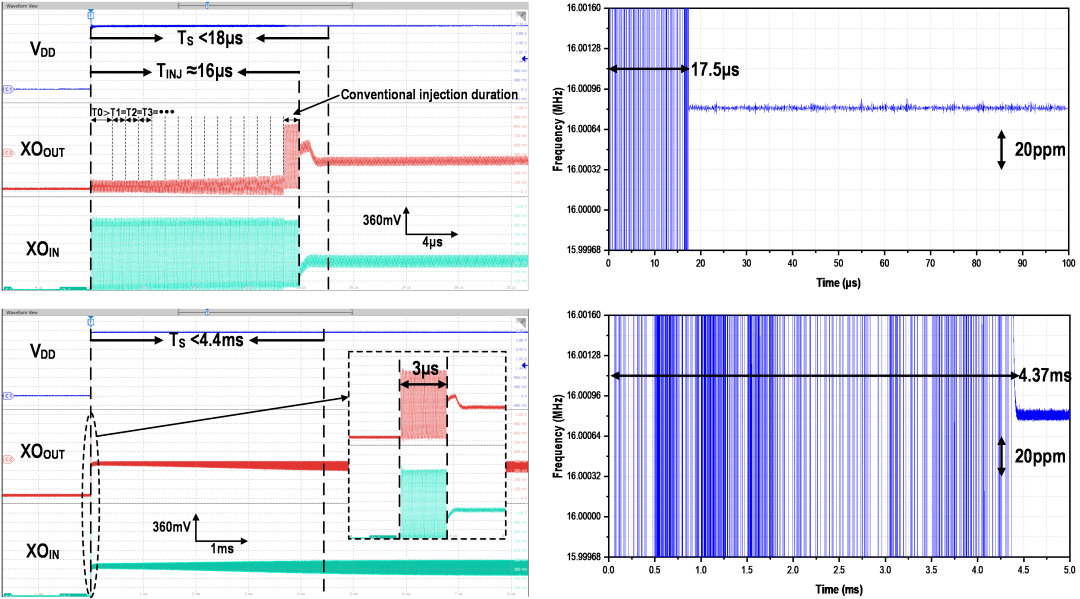

針對高頻晶體振蕩器啟動時間及注入效率問題,團隊提出了一種基于相位誤差自動校正技術的快速啟動高頻晶體振蕩器芯片架構。該款芯片沿用目前效率最高的能量注入啟動技術,首次提出相位誤差自動校正概念,并首次在高頻晶體振蕩器設計中應用單端能量注入技術。其內部電路在對高頻晶體進行能量注入的同時,檢測注入信號與晶體振蕩信號之間的相位誤差并自動校正。經流片測試驗證,在高達10000ppm(理論極限的2倍)的大頻偏注入條件下,該款芯片的實測啟動時間僅為17.5μs,將該條件下的啟動時間縮短了249倍。與傳統雙端能量注入技術相比,其啟動時間幾乎不隨注入頻率誤差波動(偏差僅為1.27%)。

這項工作首創單端注入的概念和技術,有助于更深層次的理解晶體振蕩器的啟動原理,為快速啟動晶體振蕩器設計提供了重要見解和新思路。

據悉,研究團隊一直致力于快速啟動晶體振蕩器、溫度傳感器和鎖相環等數模混合集成電路的研究與設計。此研究成果在面向物聯網應用的快速啟動晶體振蕩器領域實現突破,對進一步降低物聯網、低功耗藍牙等系統功耗意義重大。

微信二維碼

微信二維碼 網站二維碼

網站二維碼